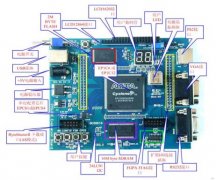

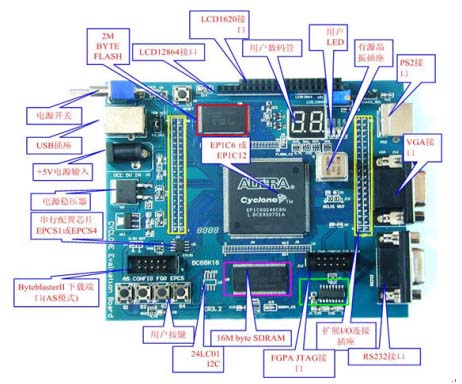

TYK-EP1C6/EP1C12 SOPC核心板

一、软件环境(WIN2000、XP) 基于QuartusII和NiosII的SOPC系统设计; SOPC Buider(定制处理器及外设接口); NiosII IDE(软件集成开发环境); 二、SOPC核心板简介 由于FPGA与存储器直接进行高速数据交换。所以成在很多干扰因素,因此这也是很多 开发板速度很难提高的关键原因。所以我们在设计的时候尽量靠近FPGA芯片。这样就*大限度减少因为布板所造成的干扰因素。 我们的开发板的SDRAM和FLASH采用独立的总线.这样就为初学者提供了更加方面灵活的设计途径.同时开发板采用了独特的跳线设计方式,可以在一块 PCB板上使用EP1C6和EP1C12两种不同容量的FPGA芯片,用户在进行设计的时候如果感觉资源不够可以 选用大容量的FPGA芯片. 1。支持EPCS1和EPCS4 EP1C6选用EPCS1配置芯片,EP1C12选用EPCS1配置芯片。 2。16M Byte 高速SDRAM 一片4M×32Bit SDRAM ,*高133MHz读写速度;MT48LC4M32B 3。2M...

分类:

描述

一、软件环境(WIN2000、XP)

基于QuartusII和NiosII的SOPC系统设计;

SOPC Buider(定制处理器及外设接口);

NiosII IDE(软件集成开发环境);

二、SOPC核心板简介

二、SOPC核心板简介

由于FPGA与存储器直接进行高速数据交换。所以成在很多干扰因素,因此这也是很多 开发板速度很难提高的关键原因。所以我们在设计的时候尽量靠近FPGA芯片。这样就*大限度减少因为布板所造成的干扰因素。 我们的开发板的SDRAM和FLASH采用独立的总线.这样就为初学者提供了更加方面灵活的设计途径.同时开发板采用了独特的跳线设计方式,可以在一块 PCB板上使用EP1C6和EP1C12两种不同容量的FPGA芯片,用户在进行设计的时候如果感觉资源不够可以 选用大容量的FPGA芯片.

1。支持EPCS1和EPCS4

EP1C6选用EPCS1配置芯片,EP1C12选用EPCS1配置芯片。

EP1C6选用EPCS1配置芯片,EP1C12选用EPCS1配置芯片。

2。16M Byte 高速SDRAM

一片4M×32Bit SDRAM ,*高133MHz读写速度;MT48LC4M32B

一片4M×32Bit SDRAM ,*高133MHz读写速度;MT48LC4M32B

3。2M Byte 通用型FLASH 可以升级到4M BYTE

一片1M×16bit(64Mbit) AM29LV160,90ns读写速度; 可以配置为16位或8位模式.

灵活的页面方式,可以用来存储FPGA配置文件或者操作系统镜像文件;

一片1M×16bit(64Mbit) AM29LV160,90ns读写速度; 可以配置为16位或8位模式.

灵活的页面方式,可以用来存储FPGA配置文件或者操作系统镜像文件;

4、板上载有一个50M有源晶振。

由于EP1C6QC240C8芯片*高运行频率80M。50M频率是可以满足大多数应用的,由于我们没有将晶振直接焊接在板上。而是通过晶振插座,所以用户能够方便的根据使用情况,更换不同频率晶振。板上所有GCLK都已经引出。如果和我们的EDA3.2主板进行搭配连接,这样就可以拥有5个以上的时钟 源,并且可以方便的更换不同时钟频率。

|

程序清单

|

||

|

HDL实验程序清单

|

||

|

1

|

\UART_IN_HDL

|

用HDL语言写的串口通讯程序

|

|

2

|

\LCD1602

|

一个LCD1602的显示试验程序.

|

|

5

|

\PS2_LCD

|

ps/2键盘输入,PS2键盘输入lcd上显示输入的字符实验

|

|

6

|

\PS2_RS232

|

实现PS/2接口与RS-232接口的数据传输,

|

|

7

|

\light

|

彩灯控制实验 实验平台上的8个LED实现常见彩灯实验。

|

|

8

|

\SRAM_TEST

|

HSNIOS1C板上的SRAM实验程序

|

|

9

|

\LED

|

板上面的LED控制程序。

|

|

NIOS部分实验程序

|

||

|

1

|

\LCD_FLASH

|

一个用NIOS写的完整的LCD演示程序.并且程序可以下载到FLASH内运行.

|

|

2

|

\UART_IN_NIOS

|

用NIOS写的开发板到PC RS232通讯实验程序

|

|

3

|

\TESTALL

|

用NIOS写的系统全检程序

|

|

4

|

\SEG7LED

|

板上的LED和数码管显示实验程序.

|

|

5

|

\ST_UCLINUX

|

一个标准Uclinux工程实验

|